Documents techniques

Spécifications

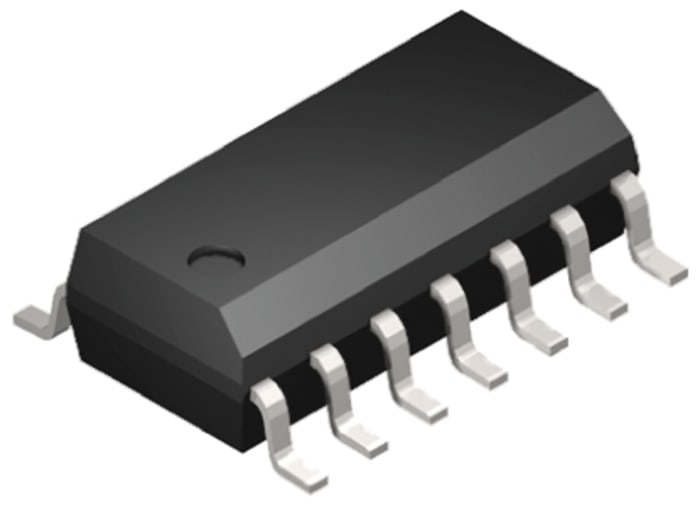

Brand

Texas InstrumentsFamille logique

LV

Fonction logique

Type D

Type d'entrée

Asymétrique

Type de signal de sortie

Differential

Type de déclenchement

Front positif

Polarité

Inverseur, Non-inverseur

Type de montage

CMS

Type de conditionnement

SOIC W

Nombre de broche

14

Set/Reset

Yes

Nombre d'éléments par circuit

2

Délai de propagation maximum @ capacité de charge maximum

20 ns @ 2.5 V

Tension d'alimentation fonctionnement maximum

5.5 V

Dimensions

8.65 x 3.91 x 1.58mm

Longueur

8.65mm

Hauteur

1.58mm

Largeur

3.91mm

Température de fonctionnement minimum

-40 °C

Tension d'alimentation de fonctionnement minimum

2 V

Température d'utilisation maximum

85 °C

Condition de test du délai du propagation

50pF

Pays d'origine

Malaysia

Détails du produit

Famille 74LV, Texas Instruments

Logique CMOS basse tension

Tension d'utilisation : 2 → 5,5

Compatibilité : Entrée LVTTL/TTL, Sortie LVCMOS

74LV Family

Prix sur demande

Each (In a Tube of 50) (hors TVA)

50

Prix sur demande

Each (In a Tube of 50) (hors TVA)

Les informations sur le stock sont temporairement indisponibles.

50

Les informations sur le stock sont temporairement indisponibles.

Documents techniques

Spécifications

Brand

Texas InstrumentsFamille logique

LV

Fonction logique

Type D

Type d'entrée

Asymétrique

Type de signal de sortie

Differential

Type de déclenchement

Front positif

Polarité

Inverseur, Non-inverseur

Type de montage

CMS

Type de conditionnement

SOIC W

Nombre de broche

14

Set/Reset

Yes

Nombre d'éléments par circuit

2

Délai de propagation maximum @ capacité de charge maximum

20 ns @ 2.5 V

Tension d'alimentation fonctionnement maximum

5.5 V

Dimensions

8.65 x 3.91 x 1.58mm

Longueur

8.65mm

Hauteur

1.58mm

Largeur

3.91mm

Température de fonctionnement minimum

-40 °C

Tension d'alimentation de fonctionnement minimum

2 V

Température d'utilisation maximum

85 °C

Condition de test du délai du propagation

50pF

Pays d'origine

Malaysia

Détails du produit

Famille 74LV, Texas Instruments

Logique CMOS basse tension

Tension d'utilisation : 2 → 5,5

Compatibilité : Entrée LVTTL/TTL, Sortie LVCMOS