Documents techniques

Spécifications

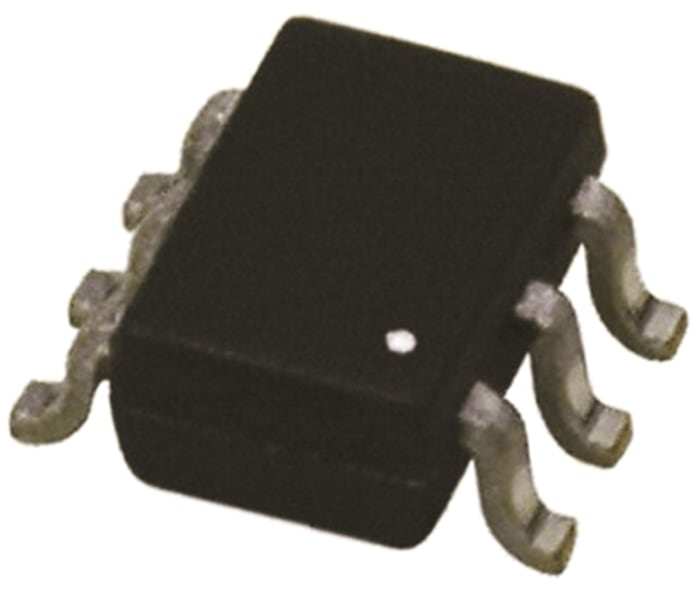

Brand

Texas InstrumentsFonction logique

Inverter

Nombre d'éléments par circuit

2

Entrée de trigger de Schmitt

No

Délai de propagation maximum @ capacité de charge maximum

4.1 ns @ 3.3 V

Courant de sortie niveau haut maximum

-32mA

Tension de sortie niveau bas maximum

32mA

Type de montage

CMS

Type de boîtier

SC-70

Nombre de broche

6

Famille logique

LVC

Dimensions

2 x 1.25 x 0.9mm

Tension d'alimentation fonctionnement maximum

5.5 V

Taille

0.9mm

Largeur

1.25mm

Tension d'alimentation de fonctionnement minimum

1.65 V

Condition de test du délai du propagation

50pF

Température de fonctionnement minimum

-40 °C

Température d'utilisation maximum

85 °C

Longueur

2mm

Détails du produit

Famille 74LVC2G, Texas Instruments

Logique CMOS basse tension

Boîtier contenant une porte

Tension d'utilisation : 1,65 à 5,5 V

Compatibilité : Entrée LVTTL/TTL, Sortie LVCMOS

74LVC Family

Prix sur demande

Each (Supplied on a Reel) (hors TVA)

Paquet de production (Bobine)

5

Prix sur demande

Each (Supplied on a Reel) (hors TVA)

Paquet de production (Bobine)

5

Les informations sur le stock sont temporairement indisponibles.

Veuillez vérifier à nouveau plus tard.

Documents techniques

Spécifications

Brand

Texas InstrumentsFonction logique

Inverter

Nombre d'éléments par circuit

2

Entrée de trigger de Schmitt

No

Délai de propagation maximum @ capacité de charge maximum

4.1 ns @ 3.3 V

Courant de sortie niveau haut maximum

-32mA

Tension de sortie niveau bas maximum

32mA

Type de montage

CMS

Type de boîtier

SC-70

Nombre de broche

6

Famille logique

LVC

Dimensions

2 x 1.25 x 0.9mm

Tension d'alimentation fonctionnement maximum

5.5 V

Taille

0.9mm

Largeur

1.25mm

Tension d'alimentation de fonctionnement minimum

1.65 V

Condition de test du délai du propagation

50pF

Température de fonctionnement minimum

-40 °C

Température d'utilisation maximum

85 °C

Longueur

2mm

Détails du produit

Famille 74LVC2G, Texas Instruments

Logique CMOS basse tension

Boîtier contenant une porte

Tension d'utilisation : 1,65 à 5,5 V

Compatibilité : Entrée LVTTL/TTL, Sortie LVCMOS