Documents techniques

Spécifications

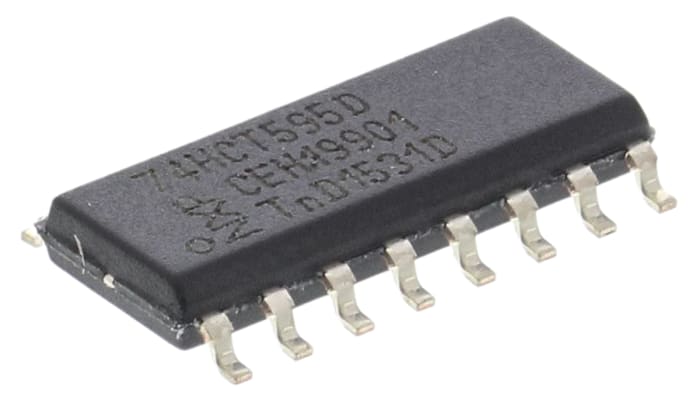

Brand

NexperiaType de boîtier

SOIC N

Fonction logique

Shift Register

Počet stupňů

8

Řada logiky

HC

Type de montage

CMS

Pracovní režim

Série vers série Parallèle

Počet prvků

1

Nombre de broche

16

Minimální provozní napájecí napětí

2 V

Tension d'alimentation fonctionnement maximum

6 V

Rozměry

10 x 4 x 1.45mm

Betriebstemperatur min.

-40 °C

Type de déclenchement

Positive Edge

Type de reset

Asynchronous

Betriebstemperatur max.

125 °C

Type de direction

Uni-Directional

Pays d'origine

China

Détails du produit

Compteurs et registres à décalage de la famille 74HC, Nexperia

Une gamme de compteurs logiques CMOS et registres à décalage NXP de la famille 74HC. La famille 74HC utilise la technologie de grille silicium CMOS pour atteindre des vitesses de fonctionnement similaires à celles de la famille LSTTL mais avec la faible consommation des circuits intégrés CMOS standards.

Logique CMOS ultra-rapide

Tension d'utilisation : 2 à 6 V

Compatibilité : Entrée CMOS, Sortie CMOS

74HC Family

Les informations sur le stock sont temporairement indisponibles.

Prix sur demande

Each (In a Tube of 50) (hors TVA)

50

Prix sur demande

Each (In a Tube of 50) (hors TVA)

Les informations sur le stock sont temporairement indisponibles.

50

Documents techniques

Spécifications

Brand

NexperiaType de boîtier

SOIC N

Fonction logique

Shift Register

Počet stupňů

8

Řada logiky

HC

Type de montage

CMS

Pracovní režim

Série vers série Parallèle

Počet prvků

1

Nombre de broche

16

Minimální provozní napájecí napětí

2 V

Tension d'alimentation fonctionnement maximum

6 V

Rozměry

10 x 4 x 1.45mm

Betriebstemperatur min.

-40 °C

Type de déclenchement

Positive Edge

Type de reset

Asynchronous

Betriebstemperatur max.

125 °C

Type de direction

Uni-Directional

Pays d'origine

China

Détails du produit

Compteurs et registres à décalage de la famille 74HC, Nexperia

Une gamme de compteurs logiques CMOS et registres à décalage NXP de la famille 74HC. La famille 74HC utilise la technologie de grille silicium CMOS pour atteindre des vitesses de fonctionnement similaires à celles de la famille LSTTL mais avec la faible consommation des circuits intégrés CMOS standards.

Logique CMOS ultra-rapide

Tension d'utilisation : 2 à 6 V

Compatibilité : Entrée CMOS, Sortie CMOS